当前位置:首页 > 技术资讯

[稳压电源]高频大功率电流源设计

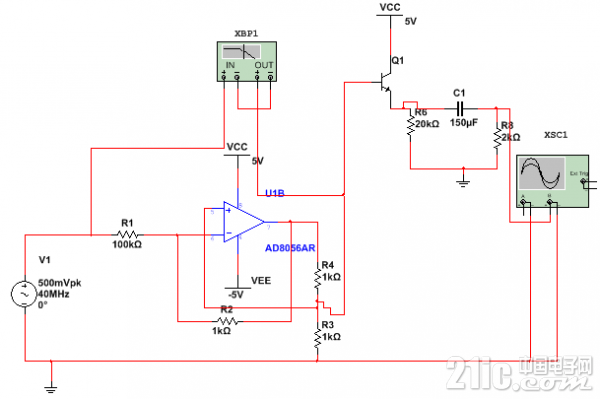

发布时间:2022-02-05 阅读:次 [打印文章] [关闭窗口]要设计一个高频大功率电流源(可以扫频),大概40MHz左右的使用频率,电流输出能力50~100mA左右,电压输出能力5V左右;我现在是先使用DDS输出扫频电压信号,然后使用OPA进行跨导放大变成恒流源,但是输出电压到500mV就上不去了,频率到1MHz左右也开始衰减了;我同时也仿真了使用高频运放来做跨导放大电流,但是运放输出电流一般比较小,电压也是500mV左右就上不去,频率特性还行;请问各位大神还有什么绝招吗?

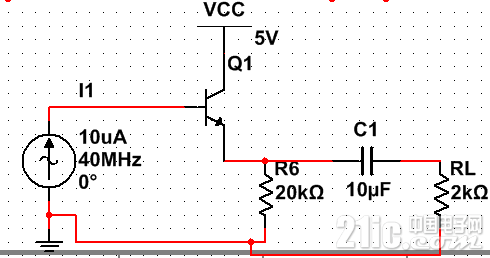

先贴图吧

做还是您做,我只能说,目前这个规格本身就不恰当,测试接头含引线(电缆)因应高频率,必须先设定固定阻抗例如50欧75歐等,而阻抗都固定了就调电压幅度即可无需转成电流源。

可以参考市面上的仪器~信号发生器。

我若讲错请以他人为准。

king5555发表于2015-12-3100:08

做还是您做,我只能说,目前这个规格本身就不恰当,测试接头含引线(电缆)因应高频率,必须先设定固定阻抗...

是什么电缆能够这么奇葩呢---1M就开始影响了,音箱线?:lol

PowerAnts发表于2015-12-3015:51

先贴图吧

现在不是电路有问题,是不知道从何下手

PowerAnts发表于2015-12-3015:51

先贴图吧

这是甲类放大雏形,但是需要有直流偏置,我偏置很小,所以负端会失真,而且这种三极管结构功率放大能用到40MHz吗

"...电压输出能力5V左右..."——这个不妥。

如此恒流100mA,恒流特性很差。

至少改成15V。

caijianfa55发表于2015-12-3111:26

这是甲类放大雏形,但是需要有直流偏置,我偏置很小,所以负端会失真,而且这种三极管结构功率放大能用到...

10uA到100mA,电流增益10000倍,达林顿管都不一定能胜任;另外R6也太大了,改用最低频率感抗千欧级的扼流圈比较适合,"无"交流分流损耗,这个RL也标错了吧,5V100mA应是50欧

幅度的问题,参考7楼,RE改用扼流圈,供电电压可减半

@king5555

BNC电缆的静电容大约每米几十pF,1MHz的容抗几千欧,因此结合6楼的RL,你逮到死耗子了.

若楼主的电路正确,跟线就没关系

PowerAnts发表于2015-12-3111:40

10uA到100mA,电流增益10000倍,达林顿管都不一定能胜任;另外R6也太大了,改用最低频率感抗千欧级的扼流...

我并不是要用这个电路来实现我的目标,我现在跨导输出的恒流源有几个毫安的负载能力,但是负载只能到两三百欧姆,负载再大电压也上不去了,如果我直接把我的恒流源后面接这种甲类放大,由于这种输入电阻非常大所以最后几乎没有输出了,而且就算有输出负半轴也会失真

PowerAnts发表于2015-12-3111:47

@king5555

BNC电缆的静电容大约每米几十pF,1MHz的容抗几千欧,因此结合6楼的RL,你逮到死耗子了.

我的意思不是你的意思,楼主想的也不一样。

我是说固定输出阻抗(如业界50欧),在对于负载50欧以上均不影响输出电压,也就是负载变动不能造成电压跟着变动。

如此输出端只要限流不让器件损坏即可,何必恒流。

输出端当然也是BNC接头的电缆线,否则如何用在40MHz。

去參考信号发生器的规格,之前有弄来一台普源制的,凑合用几次,就封装入箱,精度差了些其它还好,入他的网站都可以查到规格表。

(深夜发帖,容易表錯意,不差太多的,也懒得用改,凑合看)

想得美!插入损耗不要管了?

基于DDS+PLL技术的频率合成器的设计摘要:介绍了一种频率合成技术的设计与实现,基于DDS与PLL的技术产生高频信号频率。该频率合成器由高性能DDS芯片AD9852与锁相环芯片ADF4360-7构成。该方案控制简单、编程灵活、可靠性高,且

求一个220V交流转5V的电路图各位,求一个现成的220V交流转5V直流的电流图,要求性能稳定并且器件尽可能少,因为板子的面积很小,电路图里器件的参数最好也能提供一下,例如变压器的参数等等,要不然光有图也没用啊

高效率DC-DC转换器如何选型随着半导体技术的发展,电源稳压器的纹波越来越小,转换效率越来越高,输入电压越来越低,输出电压范围越来越广,功能日趋强大,其应用范围覆盖仪表、通信、安防及消费类电子等诸多领域,选择一款好的转换器在电源管